このページでは、QuartusIIをもちいた論理開発をどのように進めるかについて、簡単な例を用いて解説します。

QuartusIIの起動方法は二通りあります。一つは、デスクトップ上のアイコンをダブルクリックする方法で、この場合は初期画面から開始されます。もう一つの起動方法は、作業ディレクトリにすでにプロジェクトが構成されている場合、拡張子が“.qpf”となっているファイル名をダブルクリックする方法です。qpfはQuartus Project Fileの意味で、この場合はそのプロジェクトが開かれた状態で起動されます。

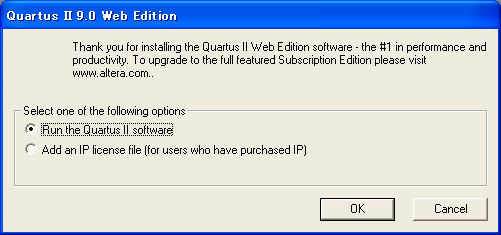

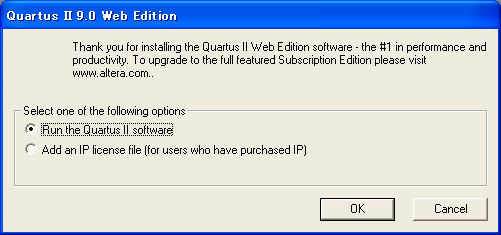

インストール後の最初の起動画面では、以下の画面が表示されます。ここでは、“Run the QuartusII software”にチェックを入れてOKを押します。

初期画面は以下のものです。左側にあるのがQuartusIIで作業を開始する場合に押すボタンで、新しくプロジェクトを作成する場合は上のボタン、すでに作られたプロジェクトを開く場合は下のボタンを押します。ここでは、最初ですので、上のボタンを押すことにします。なお、右半分は使い方の説明をみたい場合に押すボタンです。この機能を使って学習するのもよいかもしれません。

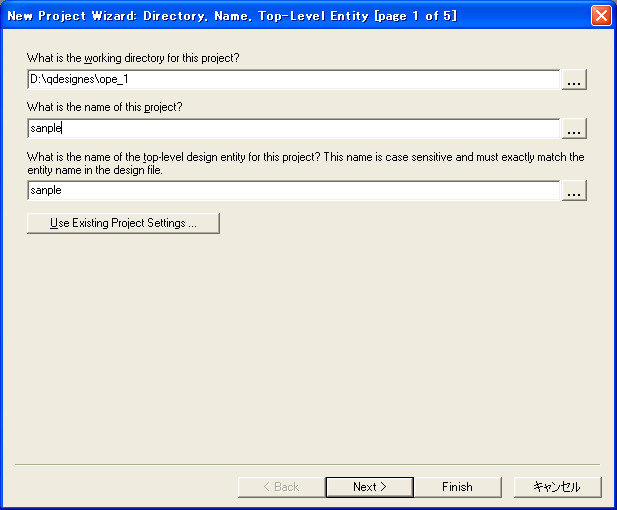

最初に、プロジェクトを作成するフォルダ(一番上のボックス)と、プロジェクト名(中央のボックス)を入力します。最下段のボックスには、最上位となるモジュール(トップ・モジュール)の名前を指定しますが、普通はプロジェクト名と同じ名前とします(そのように自動的に入力されます)。(あとで気付いたのですが、この段階でプロジェクト名を間違えて入力しています。この直し方についても、後ほど解説いたします。)

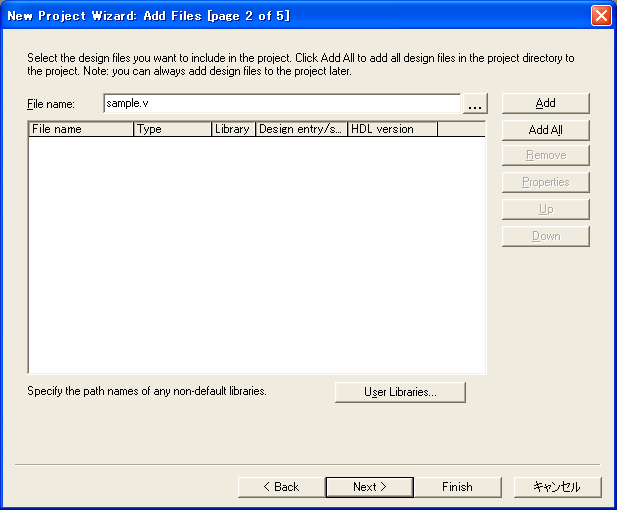

次に、プロジェクトに含めるファイル名を指定します。この指定は後からでも行うことができますので、何も指定せずに先に進んでもよいのですが、トップモジュールを定義したファイルは必ず含めることになりますので、ここで指定しておくのがよいでしょう。トップモジュールを定義するファイル名は何でもよいのですが、わたしはわかりやすいように、“プロジェクト名.v”としています。最後の“.v”はVerilogのソースファイルであることを意味します。

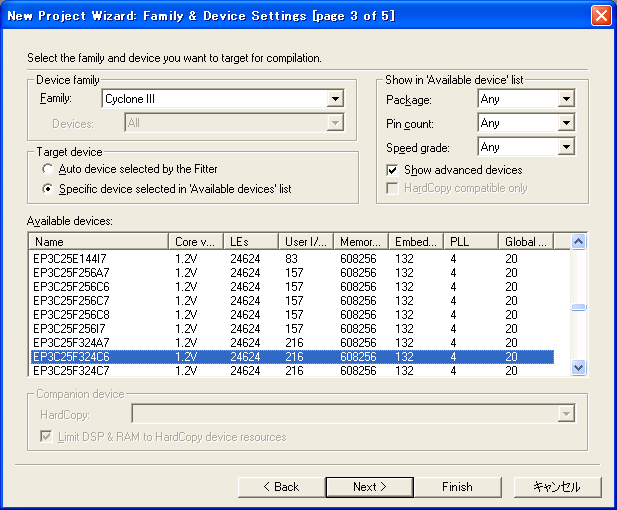

次に、ターゲットとなるFPGA(デバイス)を指定します。上のボックスにデバイスファミリーを指定します。ここでは“CycloneIII”を選択しています。ハードウエアがすでに決まっている場合は、ラジオボタン“Target Device”を“Specific device selected in 'Available devices list”にチェックを入れ、その下のリストの使用するデバイス名を反転表示させます。QuartusIIにデバイスを選ばせる場合は“Auto device selected by the Fitter”にチェックを入れます。

ここでは、Altera社の提供するCyclone III FPGA スタータ開発キットで実際のテストを行うことを念頭に、デバイス指定を行っています。なお、この開発キットは高度な仕様の割には、定価$199と、入手しやすい設定になっています。

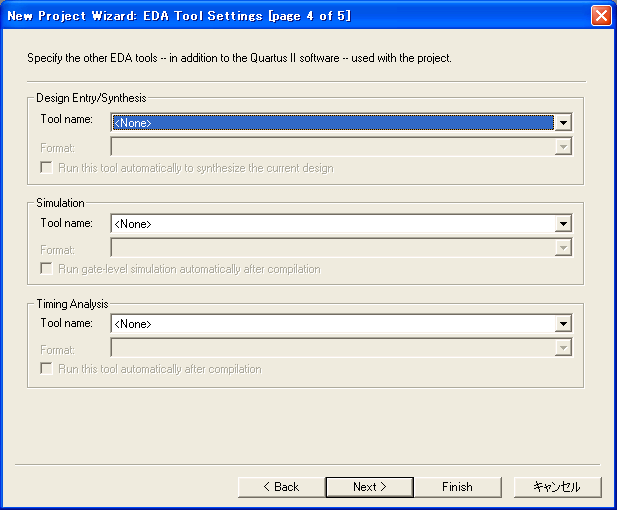

次の画面は、サードベンダの提供する開発ツールの使用を設定するもので、QualtusIIだけを用いる場合には何も記入せずにNextボタンを押します。

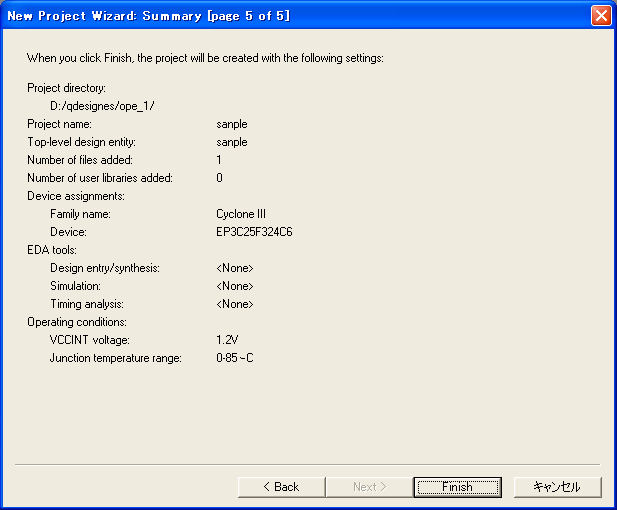

最後にこれまでの設定内容が表示されます。間違いがなければFinishを押します。

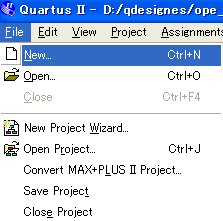

まず、Verilogのソースコードを入力します。新しくファイルを作成する場合は、プルダウンメニューのFileからNewを選択してクリックします。

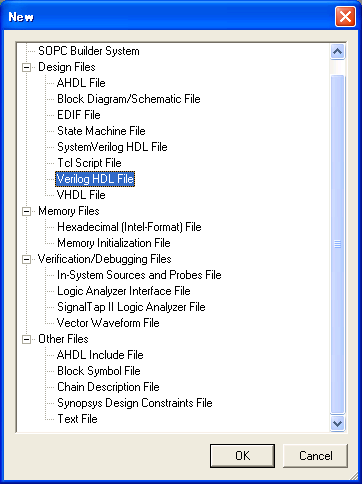

次に、作成するファイルの種類を指定します。ここでは、Design Fileの中のVerilog HDL Fileを指定します。

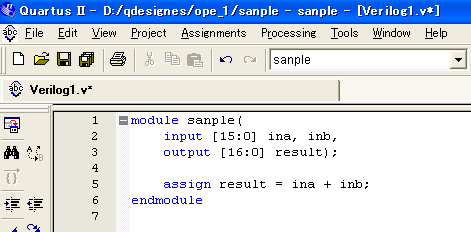

エディタ画面が開きますので、ソースコードを入力します。モジュール名はプロジェクト名と同じにします。このエディタは、予約語が青、コメントが緑で表示され、括弧の対応が色で表示されるなど、なかなかよくできたエディタです。

入力したコードはオーバーフローしない符号なし加算器です。リストを以下に示します。

module sanple( input [15:0] ina, inb, output [16:0] result); assign result = ina + inb; endmodule

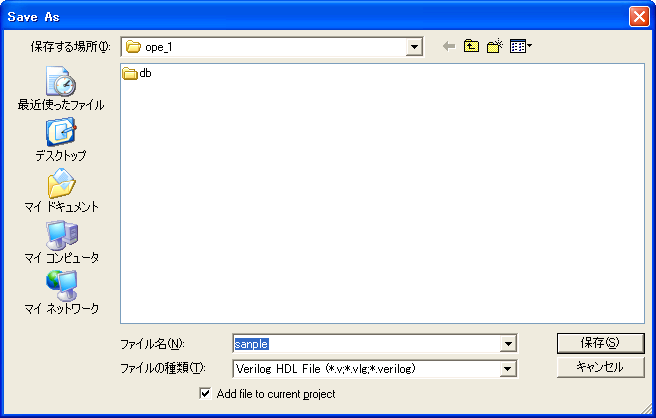

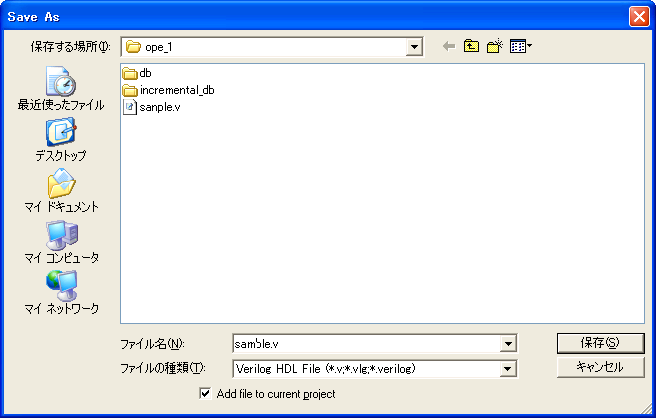

入力が完了したら、コントロール+Sを押してファイルをセーブします。この場合、ファイル名がまだ指定されていませんので、ファイル名入力画面が開きます。ここでは、ファイル名を“プロジェクト名.v”としてセーブします。

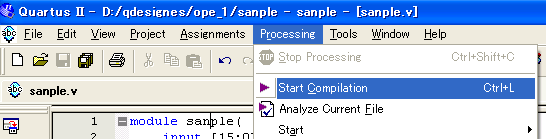

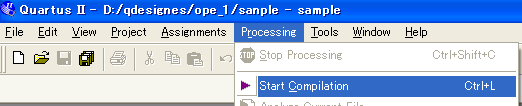

一連のコンパイル作業は、プルダウンメニューのProcessingからStart Compilationを選択して行います。

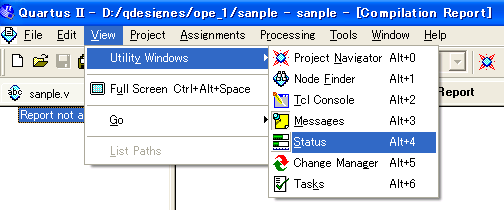

作業の進行状況は、画面最下段のウィンドウにも表示されますが、プルダウンメニューViewのUtility WindowsからStatusを押してステータス画面を表示させるのがわかりやすいでしょう。

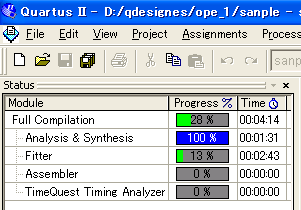

ステータス画面は以下のもので、進行状況が横棒グラフで表示されます。ここで表示されているのは、処理時間ではなく、工程数のパーセンテージですのでご注意ください。

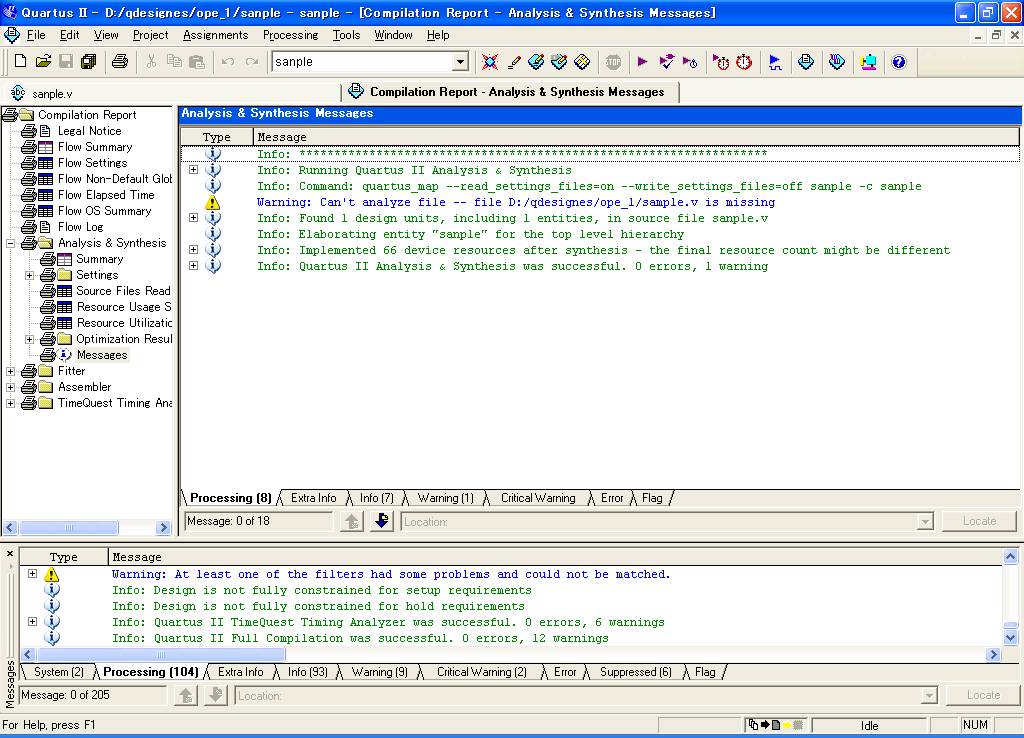

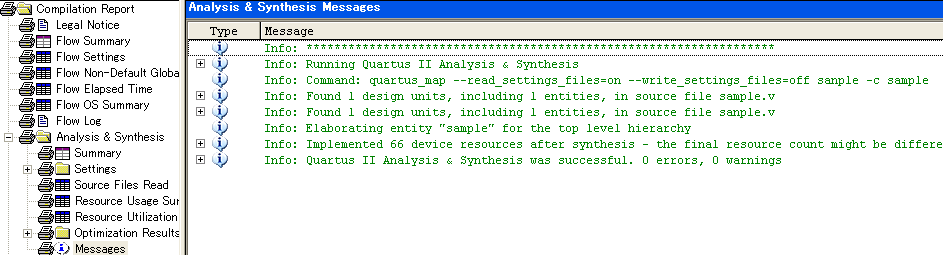

処理が完了したら、Compilation Reportを開き、Analysis & SettingのMessagesをクリックします。Compilation Reportは上部メニュー下のタブをクリックすることでも、メニューアイコンをクリックすることでも開くことができます。

Messagesでは、黄色三角が頭についたWarningに注意しましょう。ここでは、プロジェクトに含めたはずのsample.vが開けないとの警告がなされています。これは、プロジェクト名を間違えて入力したためですので、これを正しく直すことを考えましょう。

まず、ソースファイルのミススペルを直して(sanple→sample)、正しいファイル名でセーブします。元と異なるファイル名でセーブするには、他のソフトと同様、FileメニューからSave Asを選択します。

そして、正しいファイル名を指定してセーブします。

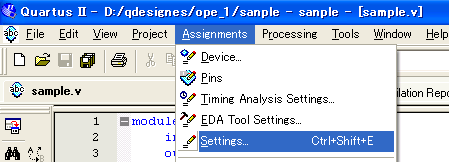

各種の設定は、プルダウンメニューのAssignmentsからSettingsを選んで行います。

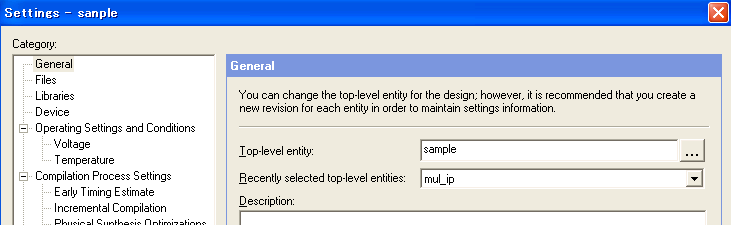

まず、トップモジュールの名前を修正します。これには、左側のボックスに表示されるCategoryのGeneralをクリックし、Top-level entityの右側のボックスに正しい名前を入力します。

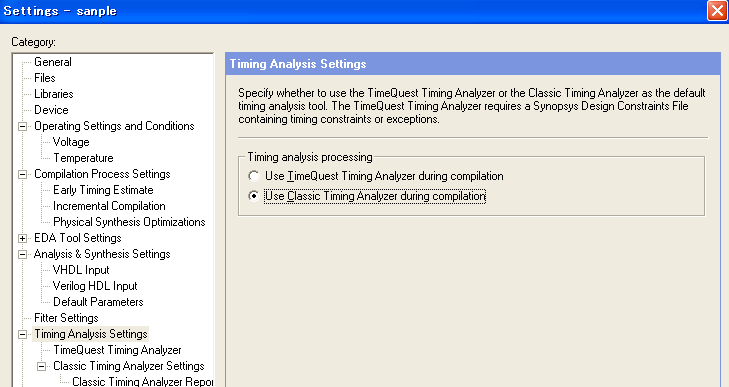

Settingsに入ったついでに、タイミングアナライザをTimeQuestからClassicに切り替えておきます。TimeQuestタイミングアナライザは比較的最近QuartusIIに加わった機能で、いろいろな解析を行ってくれるのはよいのですが、どこをみればよいのか判断に迷います。これはわたしの勉強不足でもあるのですが、初心者の方にもClassicの方がわかりやすいと思います。この切り替えは、CategoryのTiming Analysis Setting画面で、Use Classic Timing Analyzer during compilationを選択することで行います。最後はOKでセッティング画面を抜けます。

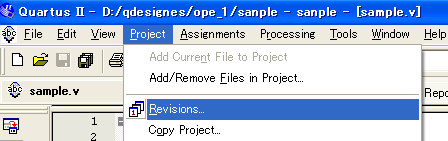

次にプロジェクト名を変更します。これは、プルダウンメニューのProjectよりRevisionsをクリックして行います。

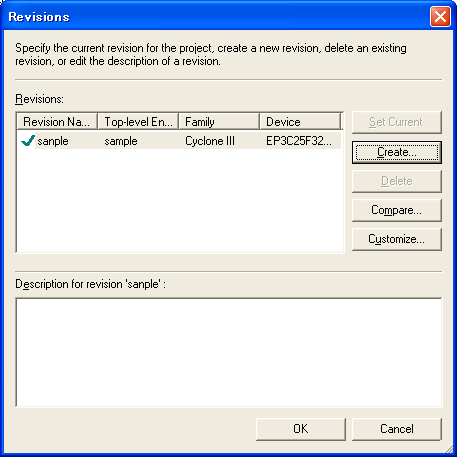

まず、ポップアップした画面右側のCeateボタンを押します。

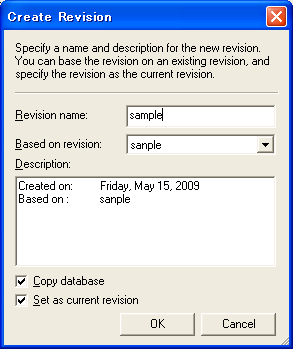

次にポップアップする画面に新しいリビジョン名を入力します。

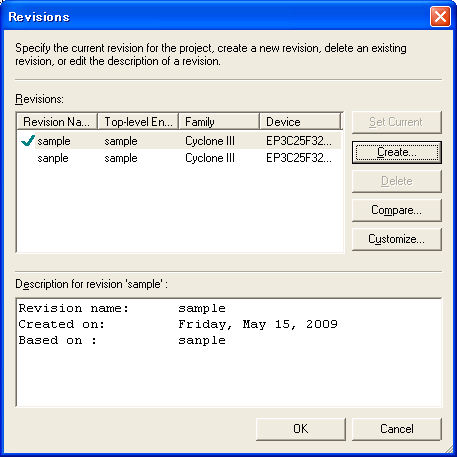

OKを押すことで元の画面に戻ります。ここで新しいリビジョンができてここにチェックが入っていることを確認してOKを押します。

新しいリビジョンで再度コンパイルします。

コンパイルが完了したら、Compilation Reportを開き、Analysis & SettingのMessagesをクリックします。今度は警告メッセージが消えています。

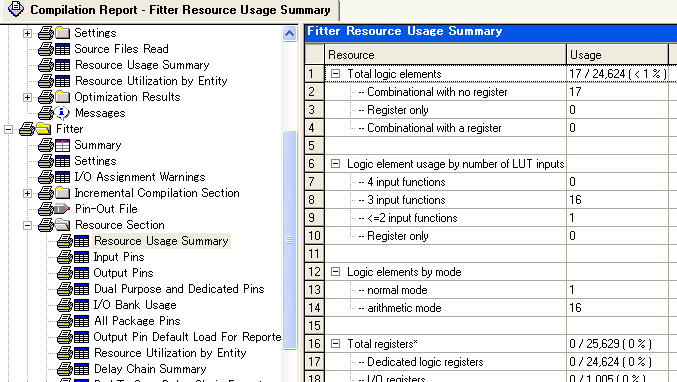

次に、FitterのResource Sectionを開き、Resource Usage Summaryを表示します。ここでは、17個のロジックエレメントが使用されていることがわかり、うち16個が3入力、1つが2以下の入力であることがわかります。今回作成したのは16ビットの加算器で出力が17ビットですから、この結果は概ね妥当なところです。

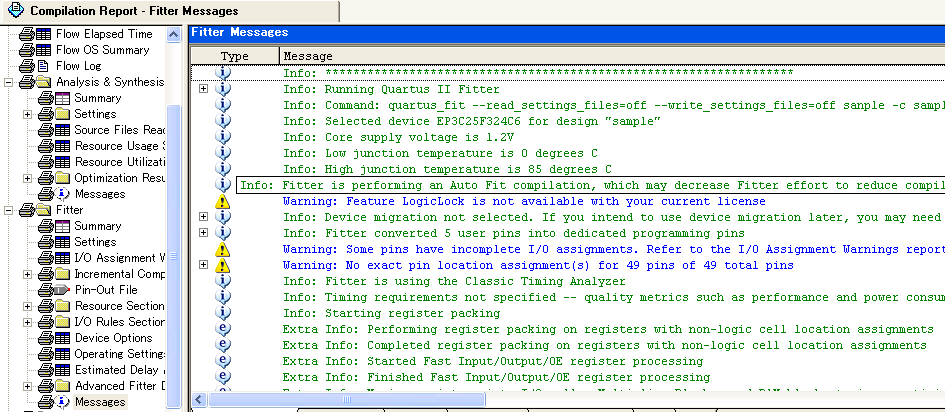

FitterのMessagesも確認しておきましょう。ここにはいくつか警告メッセージが出ています。まず、LogicLockの機能が使えないというのはWeb Editionですので当然のことであり、何も警告する必要もないように思います。また、ピンが正しく設定されていないという警告も出ていますが、今回はポートをデバイスのピンにアサインしていませんので、これも当然出てしかるべき警告です。

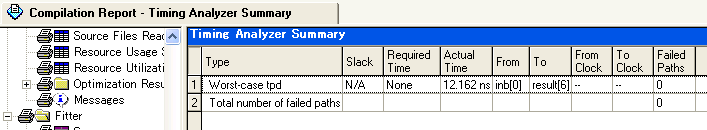

タイミングアナライザのサマリーは以下のとおりで、最大12.162nsの遅れがあると表示されています。このサマリーが威力を発揮するのはレジスタ‐レジスタ間の遅れを評価するときなのですが、今回はレジスタを使用していませんので、あまり参考にはなりません。

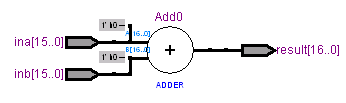

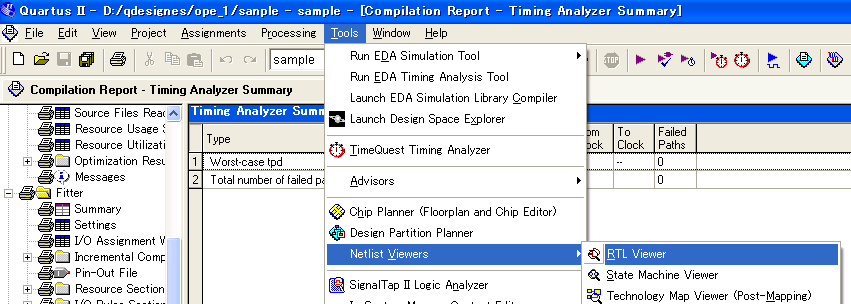

最後に回路図を表示させます。このためには、プルダウンメニューのToolからNetlist Viewersを選び、RTL Viewerをクリックします。

回路図の作成には多少の時間がかかります。最後に表示された回路は下図のとおり、確かに加算器が形成されています。